【Z80】Z80の内部構成

「【Z80】Z80の外観とピンの役割」に続き、Z80の内部を構成する主な要素とその役割を解説します。

1.Z80の内部構成

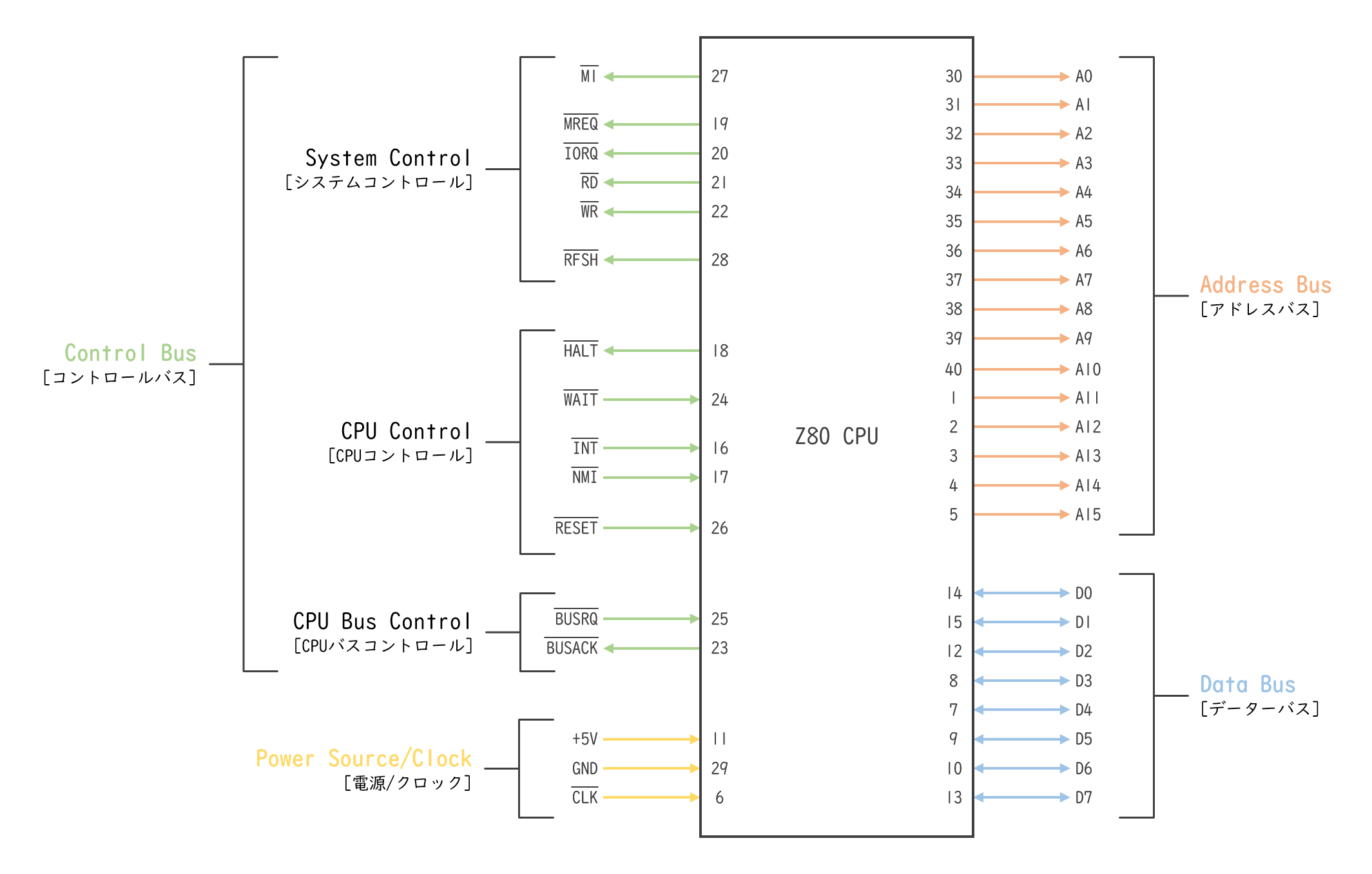

Z80と外部のメモリー、および入出力インターフェースを接続する信号線には「アドレスバス(Address Bus)」「データーバス(Data Bus)」「コントロールバス(Control Bus)」の3種類があり、それぞれ複数のピンの集まりで構成されています。(詳しい解説は「【Z80】Z80の外観とピンの役割」を参照のこと。)

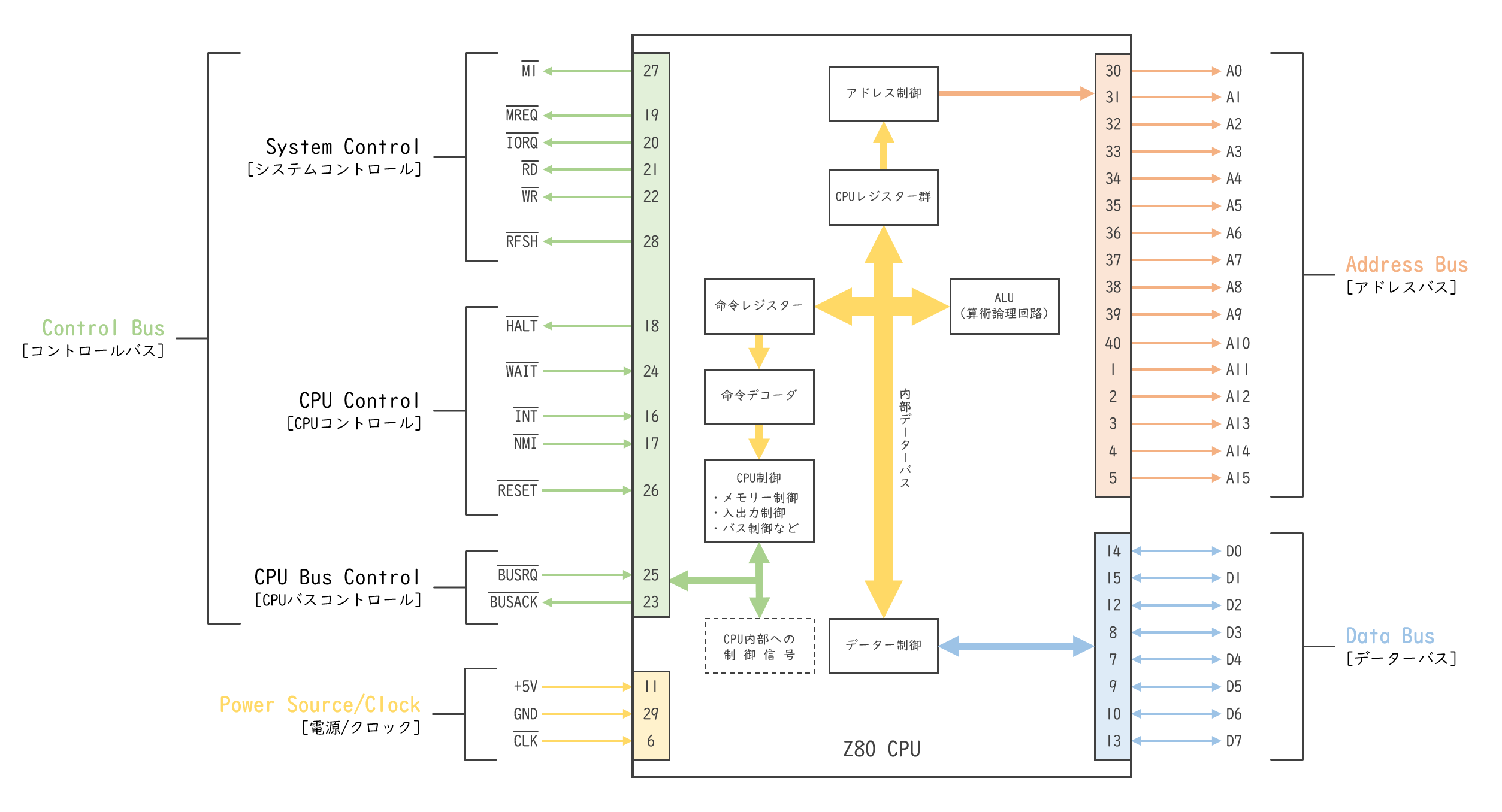

本記事では、「【Z80】Z80の外観とピンの役割」に続き、Z80の内部を構成する主な要素とその役割を解説します。図1-2は、Z80のバスと信号の向き(図1-1)に、内部を構成する主な要素を追加したものです。

「アドレスバス」「データーバス」「コントロールバス」は、それぞれ「アドレス制御」「データー制御」「CPU制御」に接続されています。その他に「CPUレジスター群」「命令レジスター」「命令デコーダ」「ALU(演算論理回路)」があり「内部データーバス」を介して、データーのやりとりが行われます。

2.内部構成の概要

CPUレジスター群

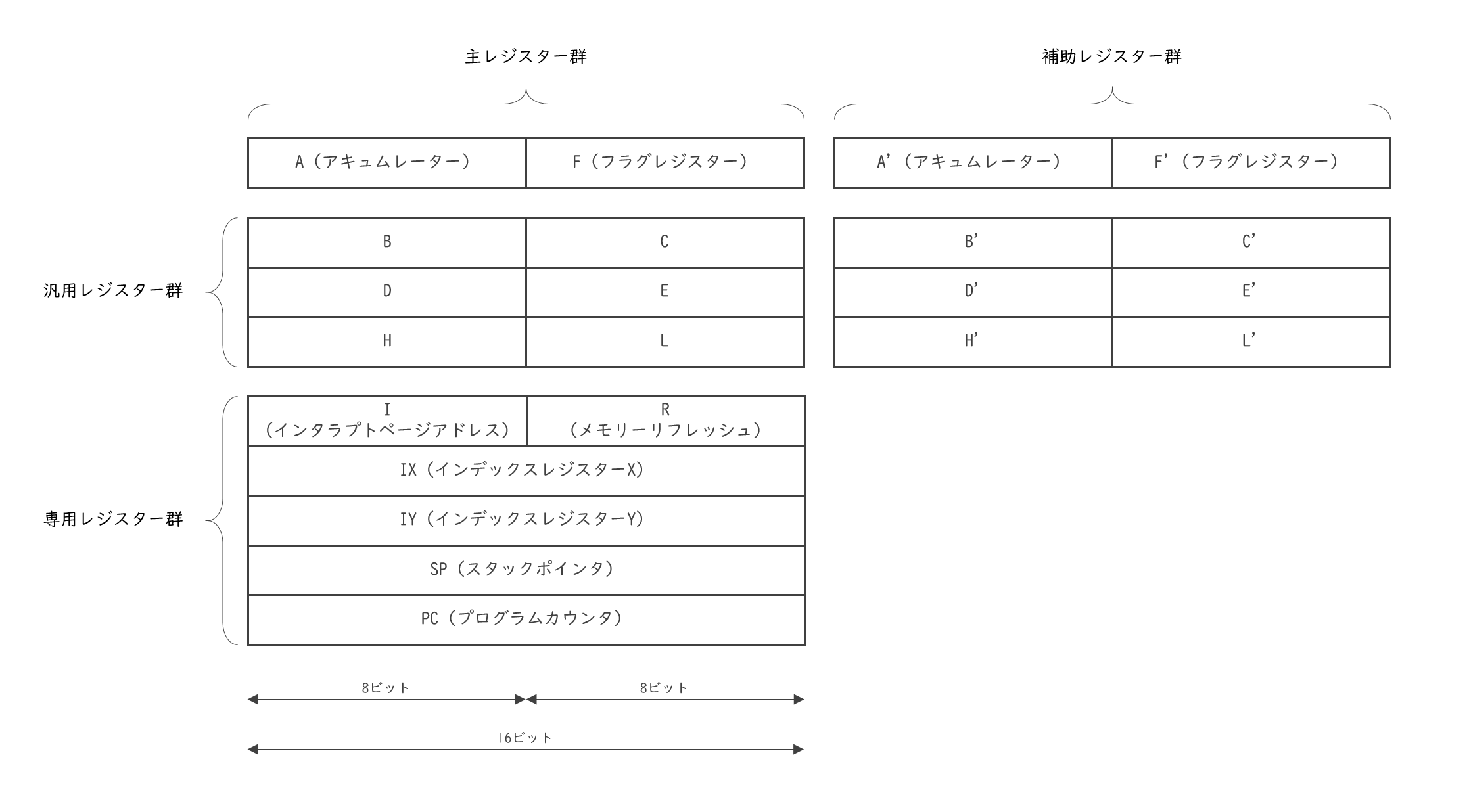

Z80の内部には、さまざまな処理で一時的にデーターを保存するためのメモリー空間があり、そのうち208ビットが公開されています。この公開されたエリアは、8ビット、または16ビットの大きさで区切られ、それぞれ「アキュムレーター」「フラグレジスター」「汎用レジスター群」「専用レジスター群」で構成されています。また、アキュムレーター・フラグレジスター・汎用レジスター群には、プログラムから直接操作できるエリア(主レジスター群)と、待避用に用いられるエリア(補助レジスター群)があります。

命令レジスター

Z80がメモリーから読み取った命令(機械語のオペコード)を一時的に保存する場所です。メモリーから命令レジスターに読み取る動作を「オペコードフェッチサイクル」といい、プログラムカウンタ(PC)の値がアドレスバスに出力され、メモリーの該当する番地のデーターが読み取られます。逆に言えば、オペコードフェッチサイクルで、メモリーからデーターバス上に出力されたデーターは、プログラマーが意図していなくても無条件に命令レジスターに読み取られ、オペコードとして解釈されます。

命令デコーダとCPU制御

命令レジスターに読み取られたオペコードは、命令デコーダによって解読されます。その後、CPU制御からALU(算術論理回路)制御・メモリー制御・入出力制御・バス制御に必要な制御信号が送出され、命令が実行されます。

ALU(算術論理回路)

ALU(算術論理回路/Arithmetic Logic Unit)では、アキュムレーターと他のレジスター、またはメモリーの内容を加算・減算・比較したり、AND(論理積)・OR(論理和)・XOR(排他的論理和)などの論理演算を行います。また、レジスターやメモリーの内容をビット単位で移動(ローテート・シフト)したり、変更(ビット操作)するのもALUの役割です。

ALUで算術、または論理演算が行われた結果、特別な意味があるものについては、フラグレジスターに記録されます。例えば、減算の結果が0の場合、フラグレジスターの7番目のビット(ゼロフラグ/Z)が1になります。

アドレス制御とデーター制御

信号の状態(Hレベル・Lレベル・ハイインピーダンス)を制御して、その状態をラッチ(保持)したり、バス上の信号の状態(データー)を読み取ります。