【Z80】YS-6464Aのメモリー空間とアクセス

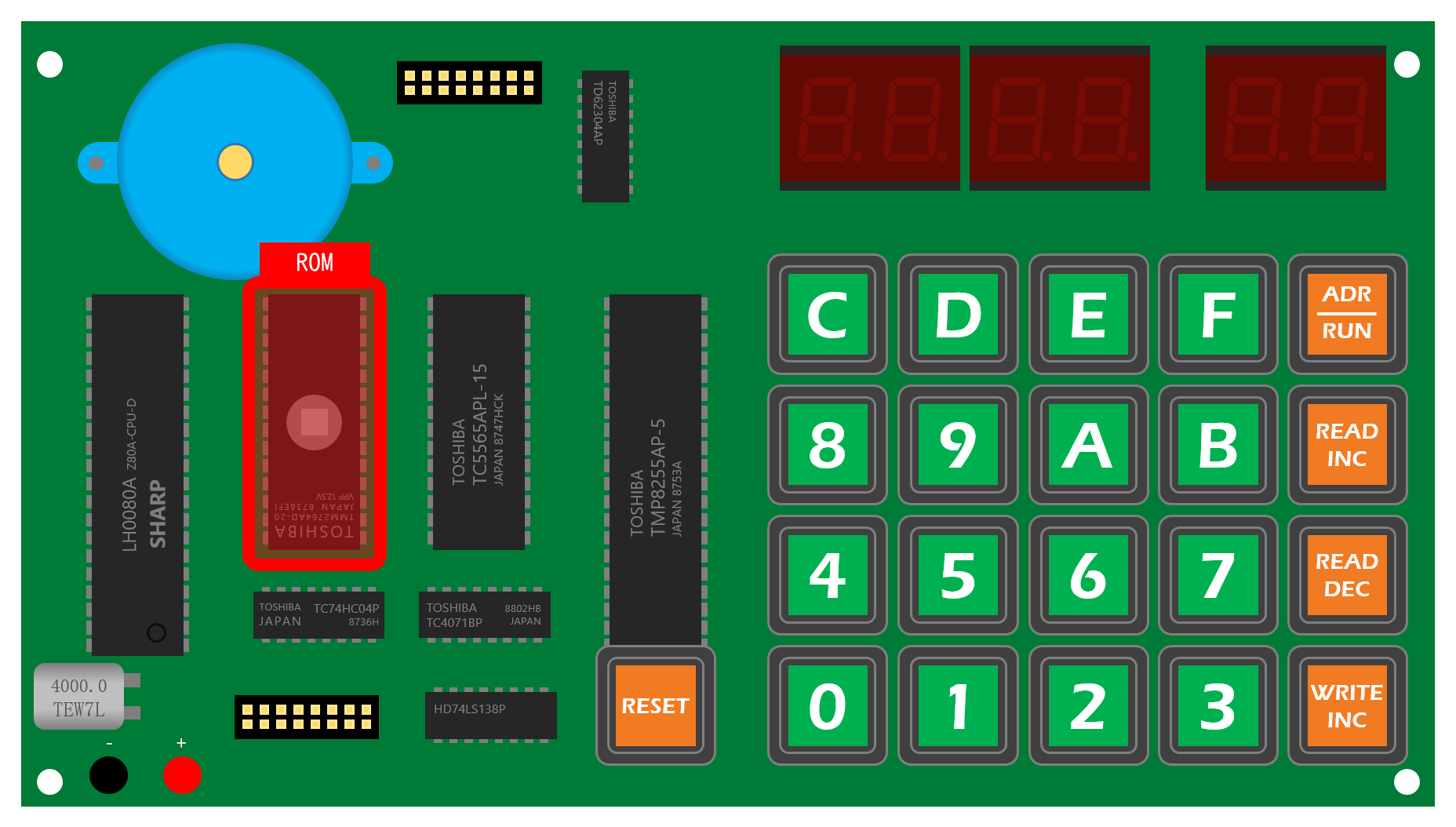

YS-6464AのROM領域・RAM領域には、それぞれ2764・5565(6264)というメモリーが実装されています。YS-6464Aのメモリー空間と、それぞれのメモリーに対するアクセスのしくみを解説します。YS-6464Aは「【Z80】Z80マイクロコンピューター「YS-6464A」」で紹介しています。

1.YS-6464Aのメモリー空間

アドレスバスとデーターバス

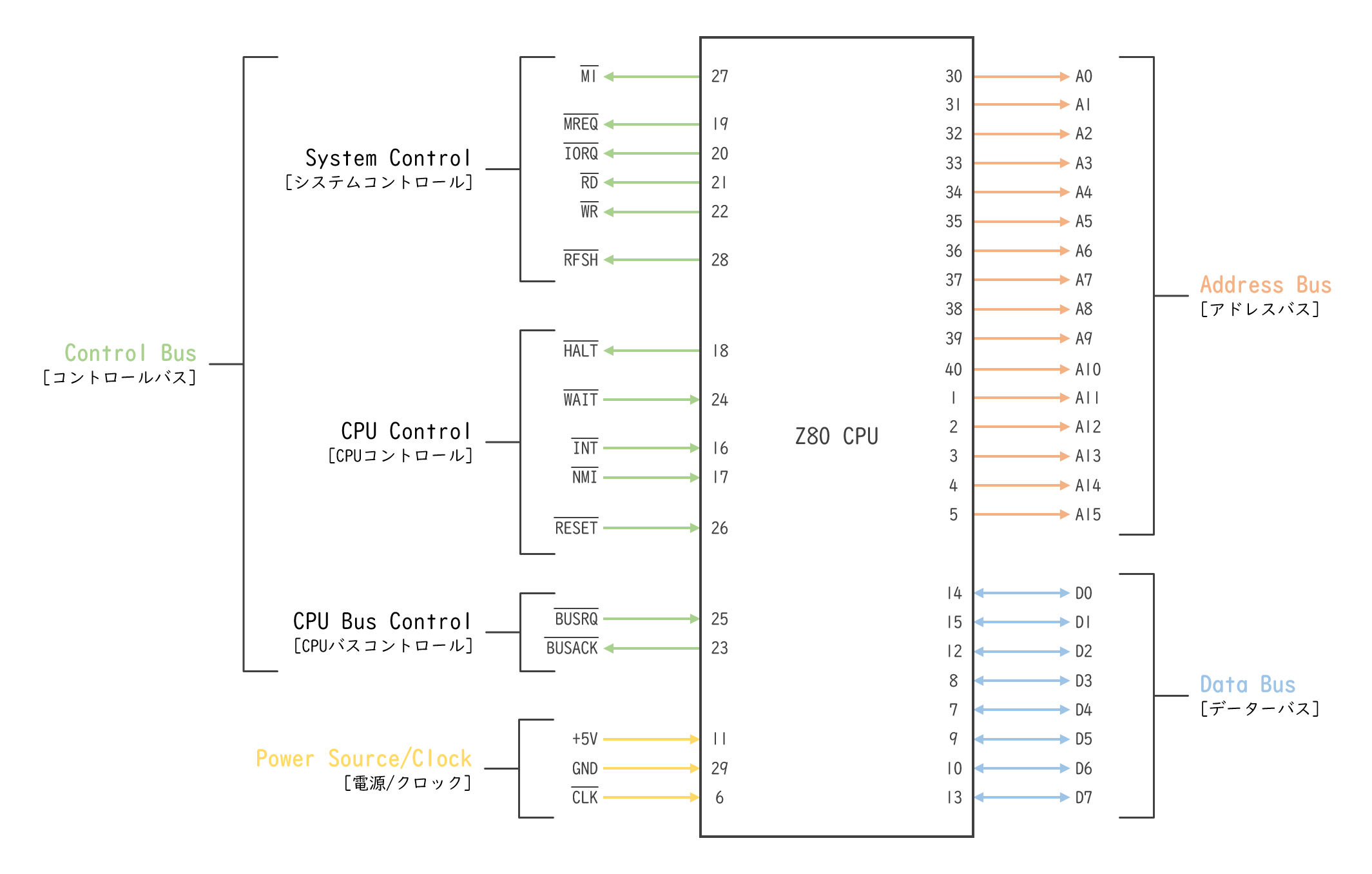

Z80では、外部のメモリーに対してデーターの場所を指定する信号線として「アドレスバス(Address Bus)」があります。また、データーは「データーバス(Data Bus)」によってアクセス(読み書き)されます。「バス」とは、複数の信号線の束を表す言葉で、Z80の場合、アドレスバスは16本・データーバスは8本で構成されています。

Z80のアドレス空間

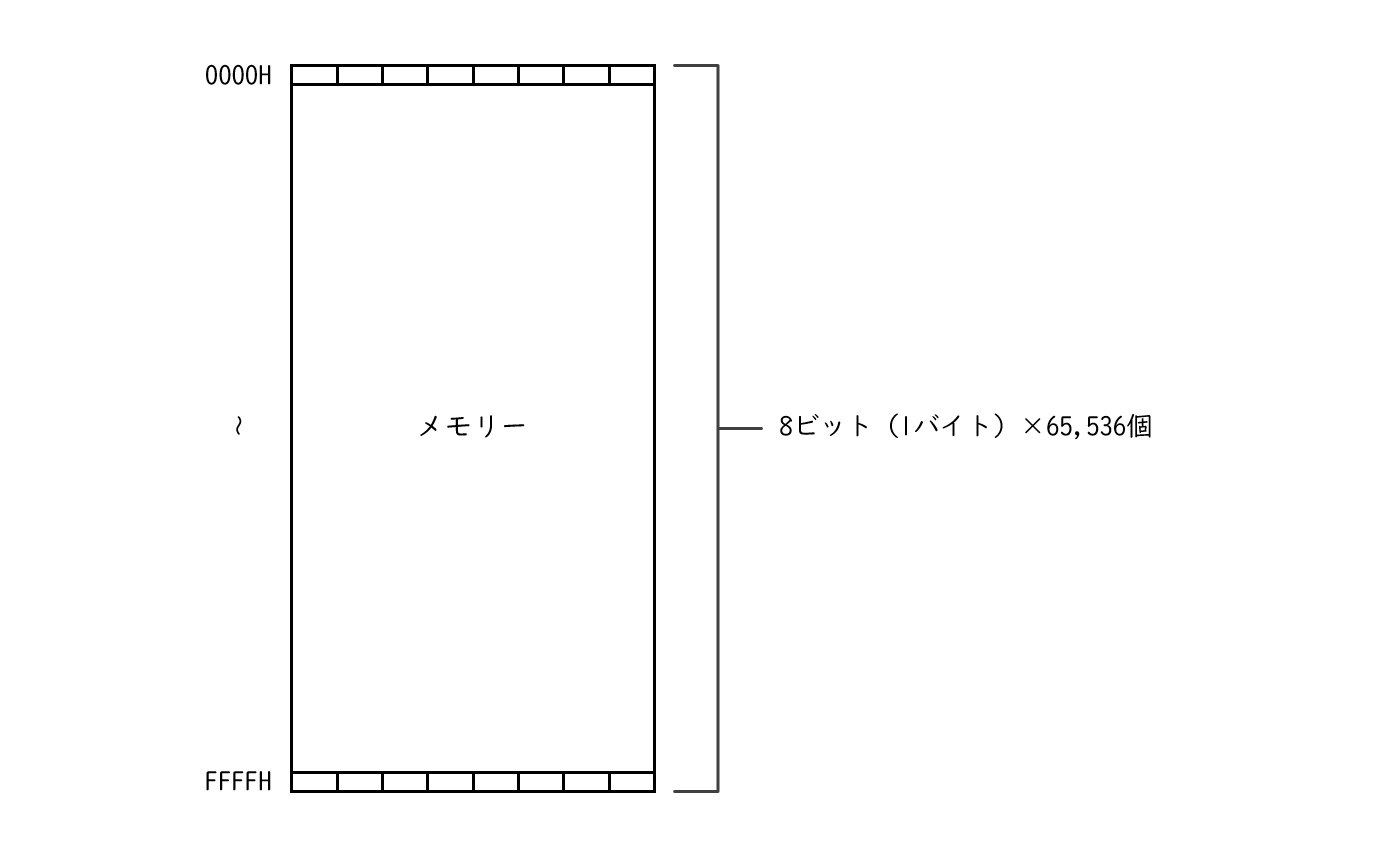

1回のアクセスで読み書きできるデーターの長さとメモリーロケーション(データーの格納エリア)の個数は、それぞれデーターバスとアドレスバスの本数に対応します。つまり、データーバス([mathjax]~\rm{D0}~[/mathjax]~[mathjax]~\rm{D7}~[/mathjax])が8本、アドレスバス([mathjax]~\rm{A0}~[/mathjax]~[mathjax]~\rm{A15}~[/mathjax])が16本なので、1回のアクセスで読み書きできるデーターの長さは8ビット(1バイト)、メモリーロケーションの個数は16ビットで表現できる「0000 0000 0000 0000(16進表記で0000H)」~「1111 1111 1111 1111(FFFFH)」までの最大65,536個となります。このアドレスバスで指定できるすべての範囲を「アドレス空間」といいます。

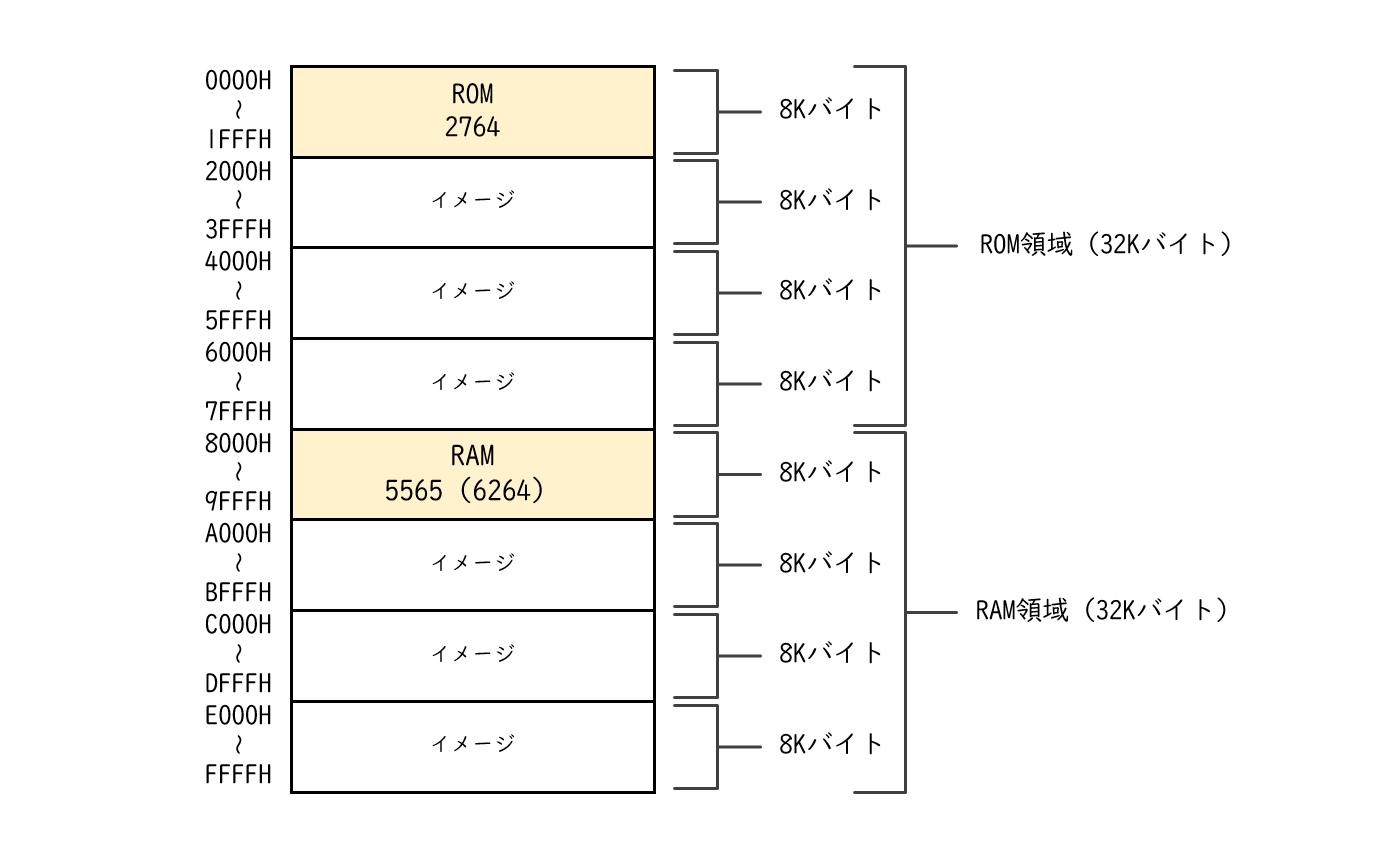

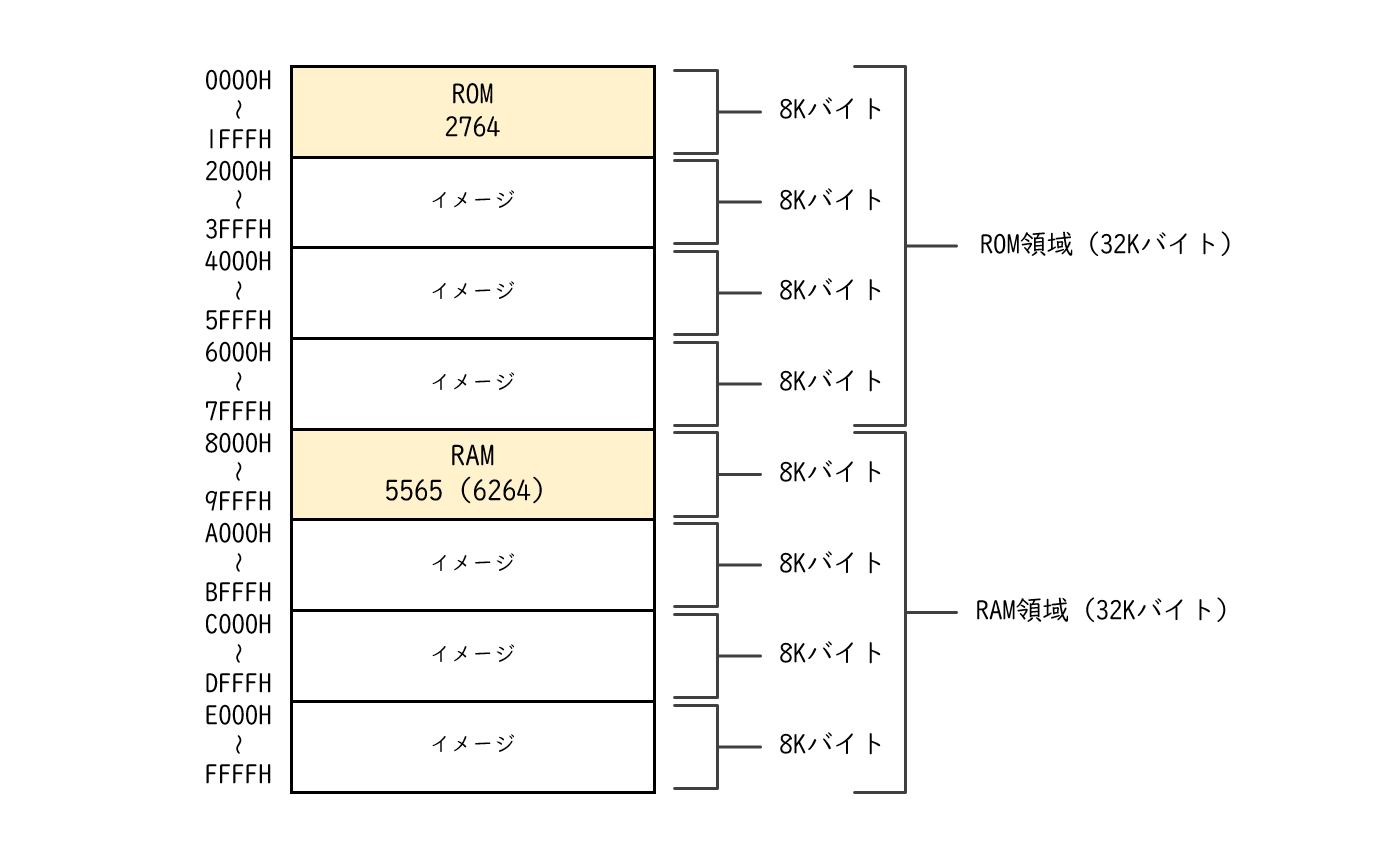

YS-6464Aのメモリー空間

Z80のアドレス空間のすべてを使うと、最大64Kバイトのメモリーにアクセスできます。ここで「最大」と表現したのには理由があります。その理由とは「メモリーの実装はアドレス空間の一部でもよい」ということです。YS-6464Aでは、64Kバイトのうち、前半の32Kバイト(0000H~7FFFH)をROM領域、後半の32Kバイト(8000H~FFFFH)をRAM領域とし、それぞれ先頭から8Kバイトのメモリーを実装しています。つまり、Z80のアドレス空間のうち、実際にメモリーが実装されたメモリー空間は、0000H~1FFFH(ROM)・8000H~9FFFH(RAM)となります。

図1-3を見ると「イメージ」と書かれた範囲があることに気づきます。このイメージとは、例えば、ROM領域の場合、メモリーの実装されている0000H~1FFFHと同じ内容が、2000H~3FFFH・4000H~5FFFH・6000H~7FFFHの3回出現することを表しています。RAM領域でも同様に、メモリーの実装されている8000H~9FFFHの内容が、A000H~BFFFH・C000H~DFFFH・E000H~FFFFHの3回出現します。また、RAM領域の場合、イメージの範囲にデーターを書き込むと、該当するメモリー(例えば、C100Hに書き込むと8100H)の内容が書き換わります。なぜこのようなことが起こるのか?その理由は後ほど。

2.メモリーの実装

YS-6464AのROM領域・RAM領域には、それぞれ2764・5565(6264)という型番のメモリーが実装されています。いずれも、容量は8Kバイト(64Kビット)です。

2764

ROM領域(0000H~7FFFH)のうち、メモリーを実装しているのは前半の8Kバイト(0000H~1FFFH)です。メモリーには、2764という型番のUV-EPROM(紫外線消去型EPROM)が採用され、あらかじめ、モニタープログラム・ユーティリティープログラム・デモプログラムが書き込まれています。また、長期にわたる信頼性を確保するために、パッケージ(黒い樹脂)上部の窓には紫外線を遮光するシールが貼られています。

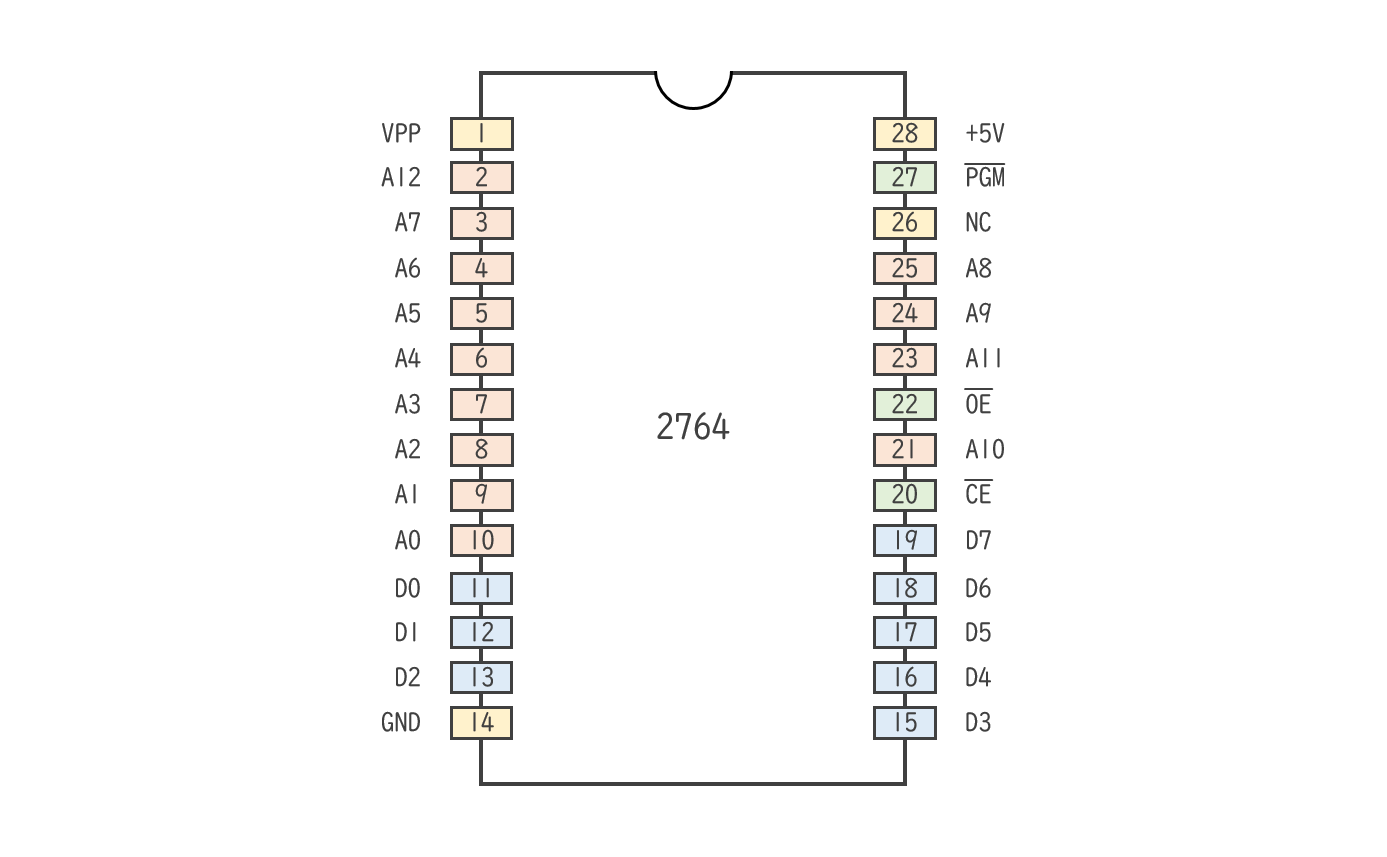

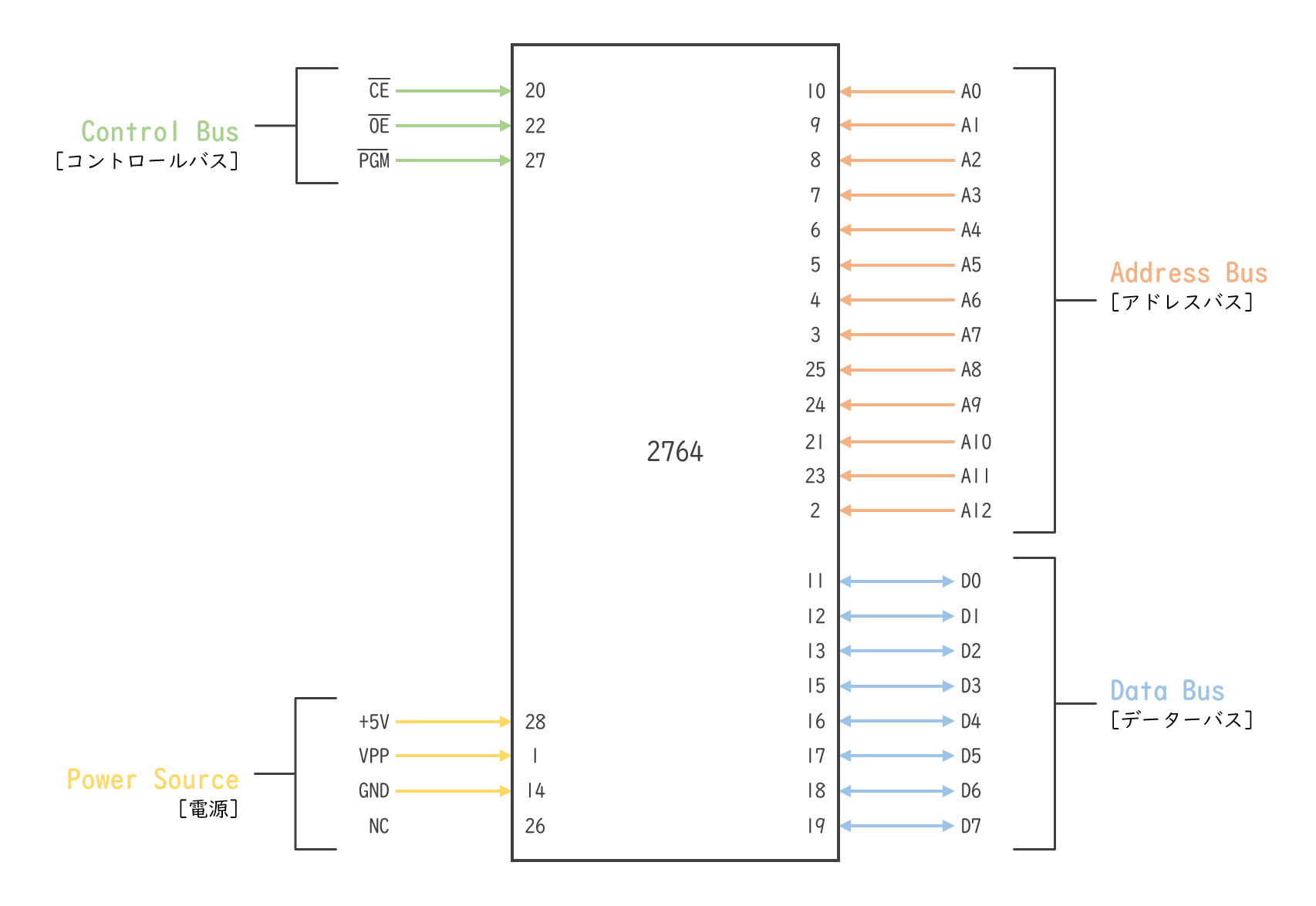

2764は、パッケージの両長辺から金属のピン(端子)がでている「DIP(Dual In-line Package)」という形状をしています。ピンの数は28ピンです。

以下に、それぞれのピンの名前と役割を簡単に紹介します。

[mathjax]~\rm{\boldsymbol{A0}}~[/mathjax]~[mathjax]~\rm{\boldsymbol{A12}}~[/mathjax]:Address bus:8Kバイトのメモリーなので、13ビット幅のバスとなります。

[mathjax]~\rm{\boldsymbol{D0}}~[/mathjax]~[mathjax]~\rm{\boldsymbol{D7}}~[/mathjax]:Data bus:8ビット幅のバスです。データーの読み出しに使用します。

[mathjax]~\rm\overline{\boldsymbol{CE}}~[/mathjax]:Chip enable:[mathjax]~\rm\overline{OE}~[/mathjax]とともにLレベルにすることでリードモードになります。Hレベルにすることでスタンバイモードとなり、[mathjax]~\rm\overline{OE}~[/mathjax]の状態に関係なく、[mathjax]~\rm{D0}~[/mathjax]~[mathjax]~\rm{D7}~[/mathjax]はハイインピーダンスとなります。

[mathjax]~\rm\overline{\boldsymbol{OE}}~[/mathjax]:Output enable:[mathjax]~\rm\overline{CE}~[/mathjax]とともにLレベルにすることでリードモードになります。

[mathjax]~\rm\overline{\boldsymbol{PGM}}~[/mathjax]:Program control:データーの書き込み時に使用するパルス信号です。

[mathjax]~\rm{\boldsymbol{+5V}}~[/mathjax]:Power source:+5Vの電源です。

[mathjax]~\rm{\boldsymbol{VPP}}~[/mathjax]:Program Power source:データーの書き込み時に使用する電源です。+21Vを印加します。

[mathjax]~\rm{\boldsymbol{GND}}~[/mathjax]:Ground:グランド(0V)です。

[mathjax]~\rm{\boldsymbol{NC}}~[/mathjax]:Non Connection / No Connecting:通常、この端子にはなにも接続しません。

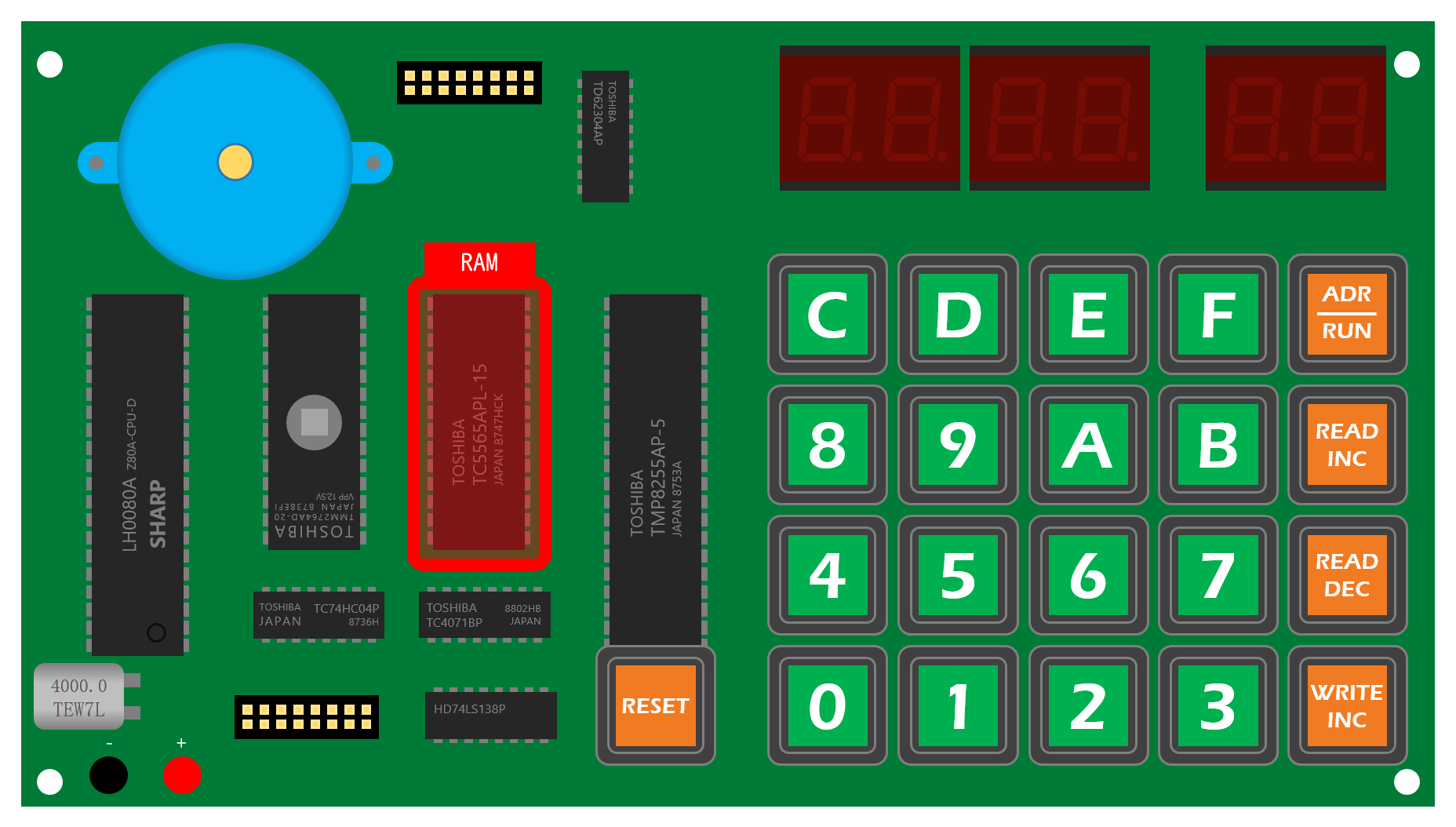

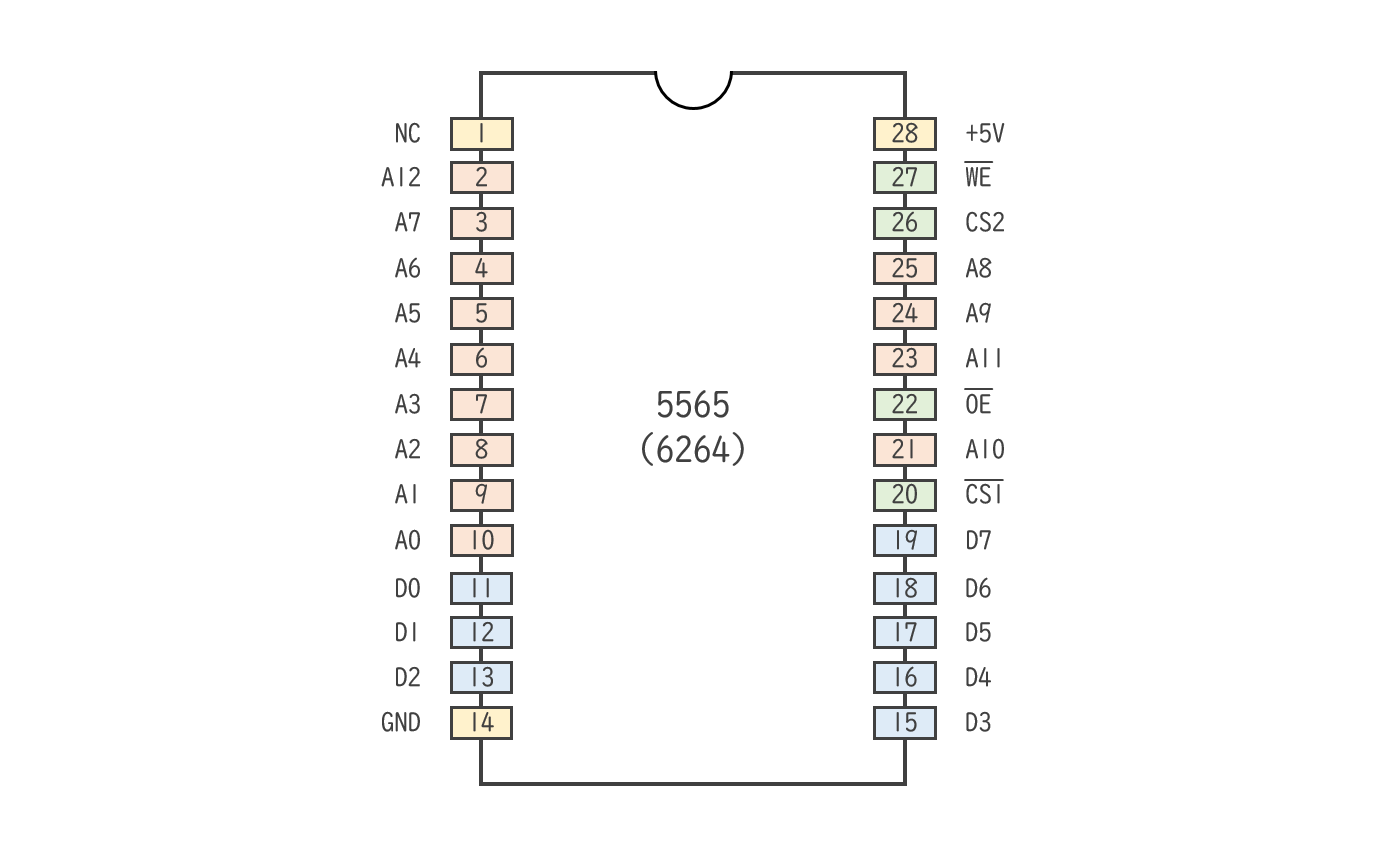

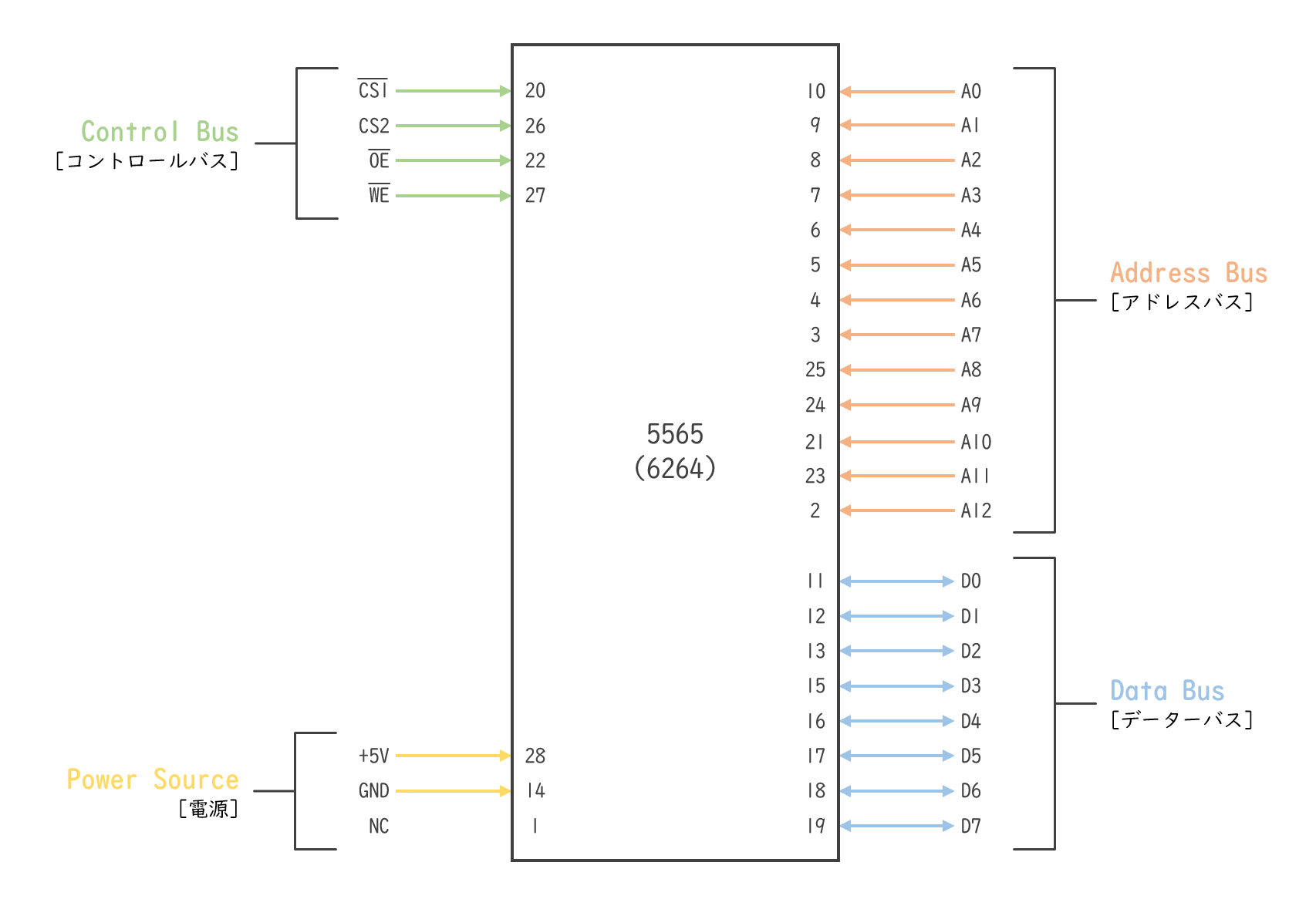

5565(6264)

RAM領域(8000H~FFFFH)のうち、メモリーを実装しているのは前半の8Kバイト(8000H~9FFFH)です。メモリーには、5565(6264)という型番のRAMが採用されています。

5565(6264)は、パッケージの両長辺から金属のピン(端子)がでている「DIP(Dual In-line Package)」という形状をしています。ピンの数は28ピンです。

以下に、それぞれのピンの名前と役割を簡単に紹介します。

[mathjax]~\rm{\boldsymbol{A0}}~[/mathjax]~[mathjax]~\rm{\boldsymbol{A12}}~[/mathjax]:Address bus:8Kバイトのメモリーなので、13ビット幅のバスとなります。

[mathjax]~\rm{\boldsymbol{D0}}~[/mathjax]~[mathjax]~\rm{\boldsymbol{D7}}~[/mathjax]:Data bus:8ビット幅のバスです。データーの読み書きに使用します。

[mathjax]~\rm\overline{\boldsymbol{CS1}}~[/mathjax]:Chip select 1:[mathjax]~\rm\overline{CS1}~[/mathjax]をLレベル、[mathjax]~\rm{CS2}~[/mathjax]をHレベルにすることで、このRAMが選択された状態になります。YS-6464Aの回路では、[mathjax]~\rm{CS2}~[/mathjax]がHレベルに固定されているため、[mathjax]~\rm\overline{CS1}~[/mathjax]のみで制御します。

[mathjax]~\rm{\boldsymbol{CS2}}~[/mathjax]:Chip select 2:[mathjax]~\rm\overline{CS1}~[/mathjax]をLレベル、[mathjax]~\rm{CS2}~[/mathjax]をHレベルにすることで、このRAMが選択された状態になります。YS-6464Aの回路では、[mathjax]~\rm{CS2}~[/mathjax]は+5Vに接続され、常にHレベルです。

[mathjax]~\rm\overline{\boldsymbol{OE}}~[/mathjax]:Output enable:RAMの選択後、Lレベルにすることでリードモードになります。

[mathjax]~\rm\overline{\boldsymbol{WE}}~[/mathjax]:Write enable:RAMの選択後、Lレベルにすることでライトモードになります。

[mathjax]~\rm{\boldsymbol{+5V}}~[/mathjax]:Power source:+5Vの電源です。

[mathjax]~\rm{\boldsymbol{GND}}~[/mathjax]:Ground:グランド(0V)です。

[mathjax]~\rm{\boldsymbol{NC}}~[/mathjax]:Non Connection / No Connecting:通常、この端子にはなにも接続しません。

3.メモリーへのアクセスのしくみ

もう一度、YS-6464Aのメモリー空間を見てみましょう。Z80のアドレス空間のうち、前半の32Kバイト(0000H~7FFFH)をROM領域、後半の32Kバイト(8000H~FFFFH)をRAM領域とし、それぞれ先頭から8Kバイトのメモリーを実装していました。つまり、実際にメモリーが実装されたメモリー空間は、0000H~1FFFH(ROM)・8000H~9FFFH(RAM)となります。

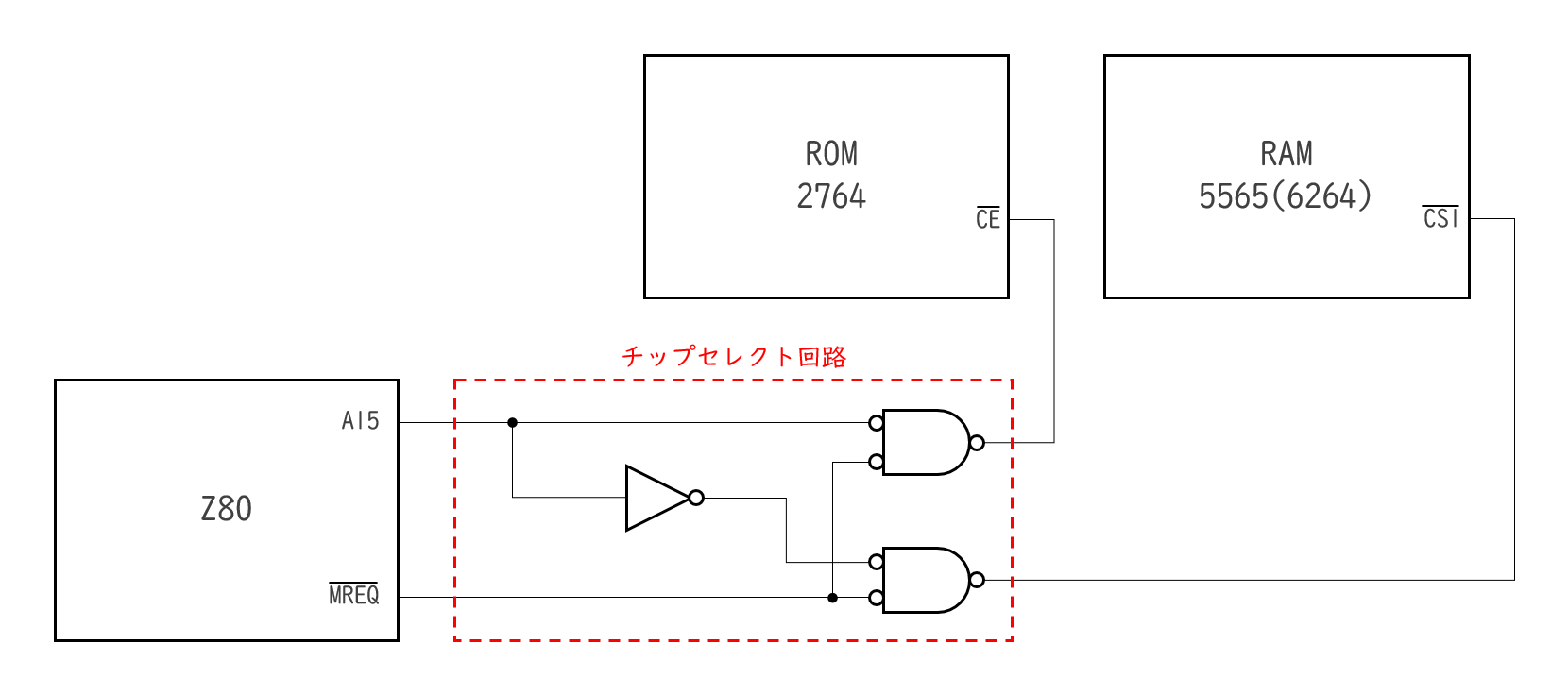

では、どのようにしてROMとRAMを切り替えているのでしょうか。実際の回路図(メモリーに関する部分の抜粋)を見ながら考えてみます。

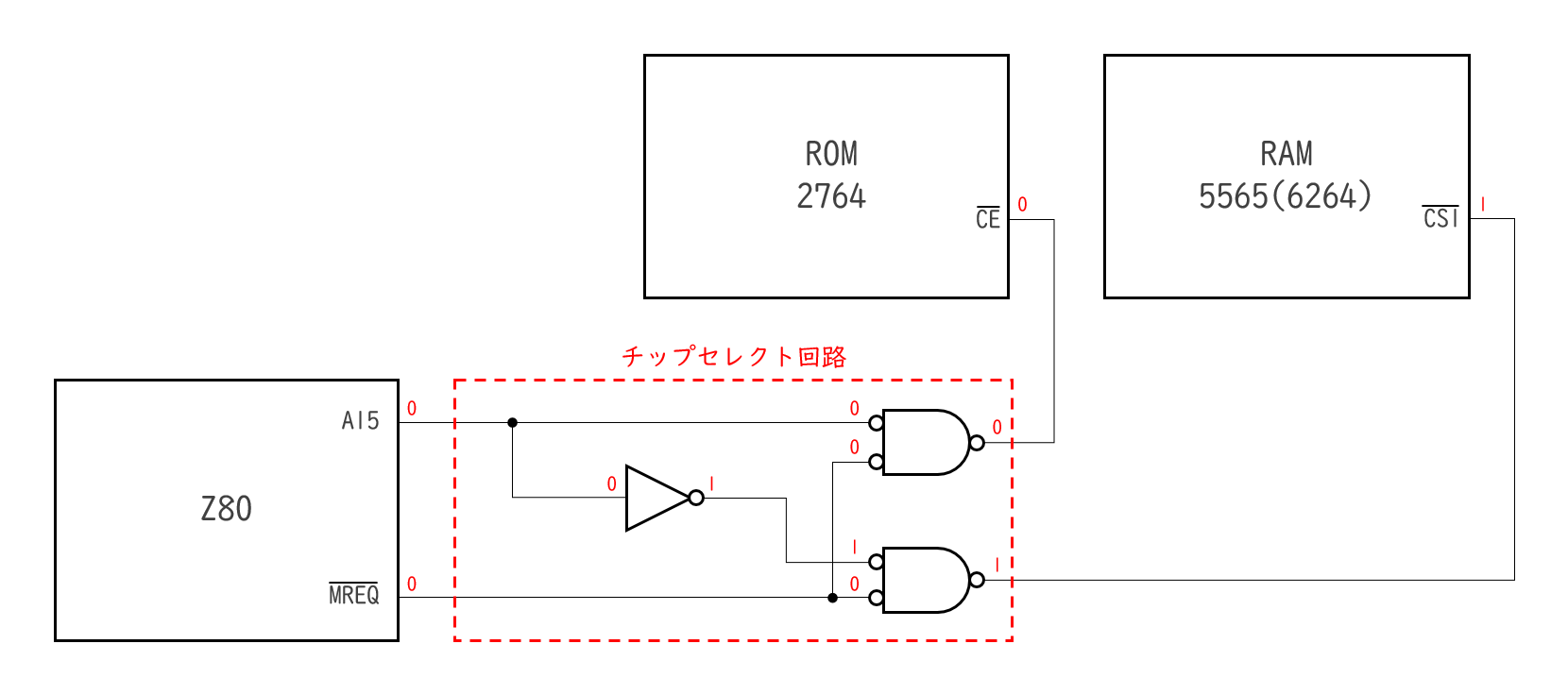

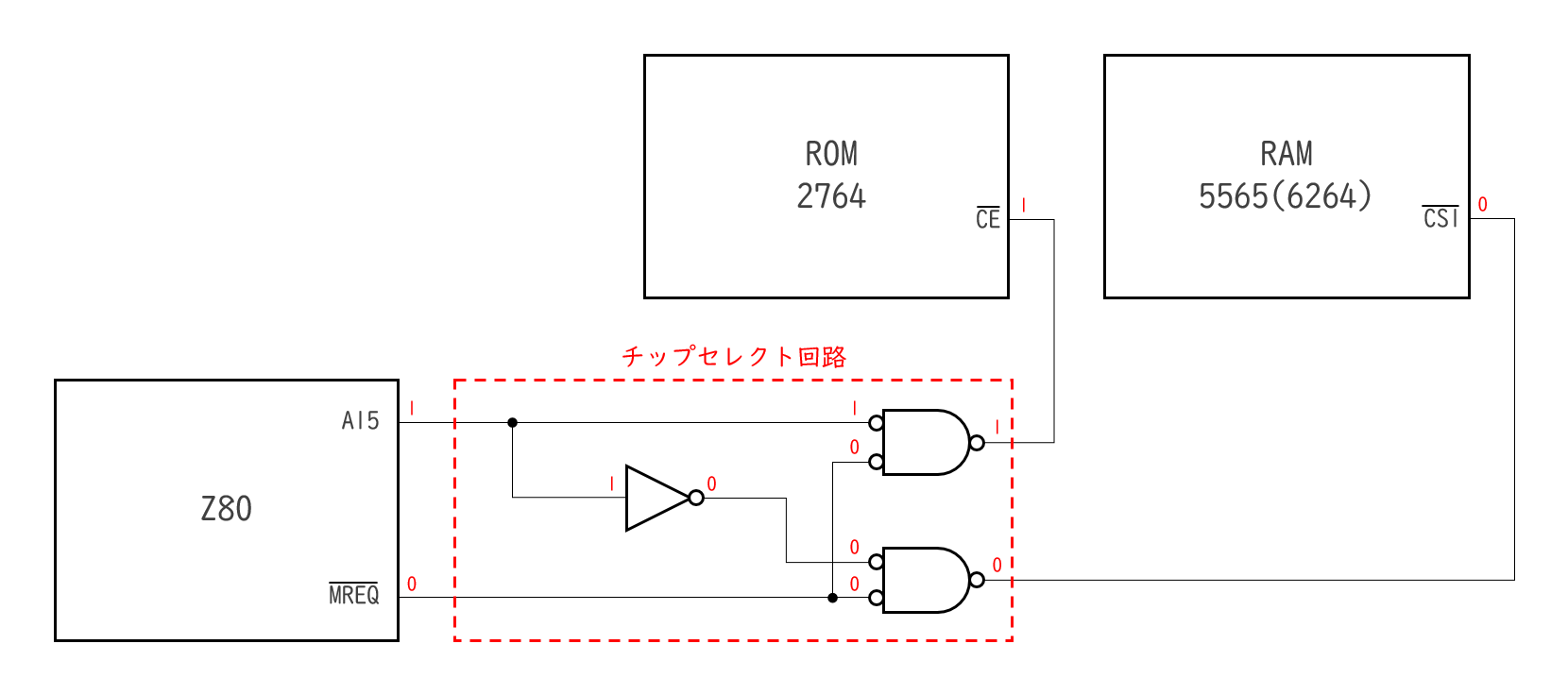

図3-2は、Z80とROM・RAMを接続する回路図です。Z80のデータバス([mathjax]~\rm{D0}~[/mathjax]~[mathjax]~\rm{D7}~[/mathjax])は、ROMとRAMに対して共通に接続されています。また、アドレスバス([mathjax]~\rm{A0}~[/mathjax]~[mathjax]~\rm{A15}~[/mathjax])のうち、[mathjax]~\rm{A0}~[/mathjax]~[mathjax]~\rm{A12}~[/mathjax]の13本が共通に接続されています。これは、いずれも8Kバイトのメモリーであり、13ビット幅のアドレスバスですべての範囲を表現できるためです。では、アドレスバスのうち、残りの[mathjax]~\rm{A13}~[/mathjax]~[mathjax]~\rm{A15}~[/mathjax]はどうなっているのでしょうか。[mathjax]~\rm{A13}~[/mathjax]と[mathjax]~\rm{A14}~[/mathjax]は未接続ですが、アドレスバスの最上位ビットである[mathjax]~\rm{A15}~[/mathjax]は、NOTゲートと2入力ANDゲート(負論理)で構成される回路に接続されています。

図3-3は、その回路を拡大したものです。この回路を「チップセレクト回路」といいます。この回路の入力には、Z80の[mathjax]~\rm{A15}~[/mathjax]と[mathjax]~\rm\overline{MREQ}~[/mathjax](Memory request)が接続されています。出力には、2764の[mathjax]~\rm\overline{CE}~[/mathjax](Chip enable)と5565(6264)の[mathjax]~\rm\overline{CS1}~[/mathjax](Chip select 1)が接続されています。[mathjax]~\rm\overline{CE}~[/mathjax]と[mathjax]~\rm\overline{CS1}~[/mathjax]は、いずれもLレベルでそのメモリーが選択された状態となります。

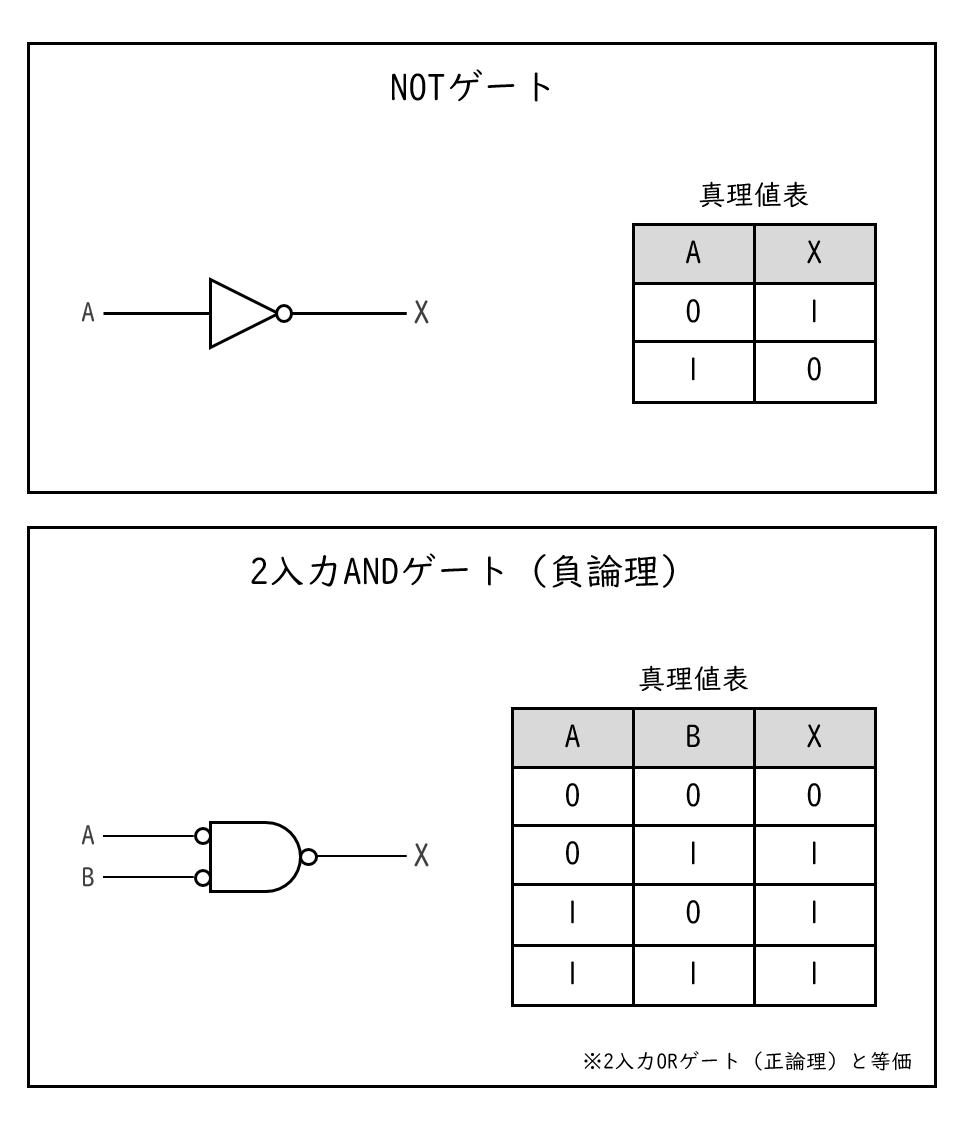

図3-4は、NOTゲートと2入力ANDゲート(負論理)の真理値表です。

では、チップセレクト回路の動作を見てみましょう。まず、ROM領域(0000H~7FFFH)にアクセスするときを考えます。アドレスが7FFFH以下の場合、アドレスバスの最上位ビットである[mathjax]~\rm{A15}~[/mathjax]は必ずLレベル(0)となります。メモリーへのアクセスを示す[mathjax]~\rm\overline{MREQ}~[/mathjax]もLレベル(0)となることから、チップセレクト回路を通った結果、2764の[mathjax]~\rm\overline{CE}~[/mathjax]がLレベル(0)、5565(6264)の[mathjax]~\rm\overline{CS1}~[/mathjax]がHレベル(1)となり、2764が選択された状態になります。

では、RAM領域(8000H~FFFFH)にアクセスするときはどうでしょうか。アドレスが8000H以上の場合、アドレスバスの最上位ビットである[mathjax]~\rm{A15}~[/mathjax]は必ずHレベル(1)となります。メモリーへのアクセスを示す[mathjax]~\rm\overline{MREQ}~[/mathjax]はLレベル(0)となることから、2764の[mathjax]~\rm\overline{CE}~[/mathjax]がHレベル(1)、5565(6264)の[mathjax]~\rm\overline{CS1}~[/mathjax]がLレベル(0)となり、5565(6264)が選択された状態になります。

このように、アドレスバスの最上位ビットである[mathjax]~\rm{A15}~[/mathjax]の状態、つまりアクセスするアドレスの範囲(0000H~7FFFH、または8000H~FFFFH)によって、選択するメモリーを切り替えています。これが、Z80のアドレス空間(0000H~FFFFH)が、前半の32Kバイト(0000H~7FFFH)と後半の32Kバイト(8000H~FFFFH)で分割されている理由です。

Z80では、メモリーにアクセスするときに使用するピンとして、アドレスバス([mathjax]~\rm{A0}~[/mathjax]~[mathjax]~\rm{A15}~[/mathjax])・データーバス([mathjax]~\rm{D0}~[/mathjax]~[mathjax]~\rm{D7}~[/mathjax])・メモリーへのアクセスを示す[mathjax]~\rm\overline{MREQ}~[/mathjax]のほかに、データーの読み込みを要求する[mathjax]~\rm\overline{RD}~[/mathjax]・データーバス上に有効なデーターを保持していること(書き込みの要求)を示す[mathjax]~\rm\overline{WR}~[/mathjax]があります。[mathjax]~\rm\overline{RD}~[/mathjax]は両メモリーの[mathjax]~\rm\overline{OE}~[/mathjax](Output enable)、[mathjax]~\rm\overline{WR}~[/mathjax]は5565(6264)の[mathjax]~\rm\overline{WE}~[/mathjax](Write enable)に接続されています。

Z80のアドレスバス([mathjax]~\rm{A0}~[/mathjax]~[mathjax]~\rm{A15}~[/mathjax])のうち、[mathjax]~\rm{A0}~[/mathjax]~[mathjax]~\rm{A12}~[/mathjax]と[mathjax]~\rm{A15}~[/mathjax]のみがメモリーのアクセスに使用されています。つまり、未接続の[mathjax]~\rm{A13}~[/mathjax]と[mathjax]~\rm{A14}~[/mathjax]がどのような値になっても、結局[mathjax]~\rm{A0}~[/mathjax]~[mathjax]~\rm{A12}~[/mathjax]と[mathjax]~\rm{A15}~[/mathjax]で示されるアドレスにアクセスするということになります。これが、イメージの出現する理由です。

本記事で紹介したチップセレクト回路は、YS-6464Aで採用されている回路です。システムが異なれば、また違ったチップセレクト回路が見られます。

![図3-7.[mathjax]~\rm\overline{RD}~[/mathjax]と[mathjax]~\rm\overline{WR}~[/mathjax]](/and-more/images/z80/ys-6464a-memory-map/ys-6464a-memory-map-16.png)